ADGS1408/9 SPI Multiplexers - Analog Devices | DigiKey

2018年8月13日 · A serial peripheral interface (SPI) controls the switches. The SPI has robust error detection features such as cyclic redundancy check (CRC) error detection, invalid read/write address detection, and SCLK count error detection.

Analog switches & muxes | TI.com - Texas Instruments

Our high quality analog switches and multiplexers (muxes) maintain signal integrity with our broad range of voltage, configuration and package options. Reduce design complexity and optimize system cost in precision measurements, power sequencing, and I2C, SPI, JTAG and general-purpose signals.

[FAQ] TMUXS7614D: What is a SPI Controlled MUX? - Switches ...

2024年9月17日 · The TMUXS7614D is TI’s first true SPI controlled mux. It is a 1:1, single-pole, single-throw (SPST) 8-channel SPI controlled multiplexer. The SPI signal communication is defaulted to address mode, where the registers of the mux are accessed by a 16-bit SPI command bounded by the chip select line (/CS).

ADGS1208 Datasheet and Product Info | Analog Devices

2018年4月2日 · A serial peripheral interface (SPI) controls the switches. The SPI interface has robust error detection features, such as cyclic redundancy check (CRC) error detection, invalid read/write address detection, and SCLK count error detection.

TS3A44159: SPI Mux - Switches & multiplexers forum - TI E2E …

The SN74CB3Q3257 and the TS3A44159 can both be used for SPI bus depending on you voltage supply. Another great option is to use the newly released TMUX1574, which calls out SPI bus multiplexing on the front page and in the applications section.

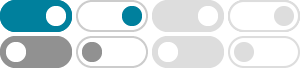

With the SPI Multiplexer it can be done with a single chip. Instead of GPIOS, it has an internal SPI (as shown in Figure 1-1) allowing for independently controlling the switches, resulting in a smaller footprint design. Figure 1-1. SPI Controlled Multiplexer.

Introduction to SPI Interface | Analog Devices

This article provides a brief description of the SPI interface followed by an introduction to Analog Devices’ SPI enabled switches and muxes, and how they help reduce the number of digital GPIOs in system board design. SPI is a synchronous, full duplex main-subnode-based interface.

serial peripheral interface (SPI) protocol, routed by a multiplexer (MUX). Figure 1 shows how a MUX routes the SPI signal to give users multiple ways to access the flash memory, either through the FPGA or an external header. The header allows external access to the flash memory to debug boot-up code and to update other stored firmware. 2:1 MUX ...

SPI Mux/Decoder/Expander - TI E2E support forums

If SPI master's driving strength is capable of handling 60 SPI slaves, what you need is to multiplex CS0~CS7. Using 8 unit of SN74CBTLV3251 or SN74LV4051A, 1:8 de-multiplexer, or 4 unit of CD4097B, 2-channel, 1:8 de-multiplexer, should be enough.

1. SPI interface removes the need for parallel conversion, logic traces, and reduces the general-purpose input/output (GPIO) channel count. 2. Daisy-chain mode removes additional logic traces when multiple devices are used. 3. CRC error detection, invalid read/write address detection, and SCLK count error detection ensure a robust digital ...