How do D flip-flops (dff) start up in Quartus?

Aug 26, 2019 · If I connect Q0 of one dff to its D0, its Q0 stays 0. But if I take another dff and connect its Q1 with Q0 of the first dff through OR to his D1, its Q1 stays 1. I understood that all …

2.1. Step 1: Create Simple Flip-Flop Design - Intel

Follow these steps to define and synthesize the flip-flop logic to generate the IOE: Create a new project in Intel® Quartus® Prime Pro Edition software version 21.3. Click Assignments > …

DFF Primitive - Intel

The DFF primitive allows you to program a register as an edge-triggered D flipflop. Note: For information about Quartus ® Prime primitive instantiation, go to Using a Quartus ® Prime …

Flip Flop Simulation Files in Quartus : r/EngineeringStudents

Mar 17, 2015 · The CLRN, PRN, and D signals are all inputs to the flip-flop, and the output is Q. Each input can be forced either high or low whenever you want. The main input that is used …

VHDL behavioural D Flip-Flop with R & S - Stack Overflow

Jan 5, 2016 · Flip flops in FPGA devices usually have either asynchronous set or reset, but not both, so Altera Quartus tries to make the requested circuit with latches instead of dedicated …

It explains how to design, compile, simulate and program. your logic designs in the Quartus II software using a D-Flop. according to the UP3 board layout. In this particular case, the D. …

question about D flip-flop - Intel Community

Sep 22, 2011 · Hi all, I am wondering what does the PRN port in the D flip-flop used for? When PRN is deasserted, the output always stay asserted.Thanks!

positive edge-triggered D-type flip-flops - Intel Communities

Apr 29, 2010 · how do i code a positive edge-triggered D-type flip-flops in AHDL or VHDL?? 04-29-2010 06:47 AM. If you use Quartus II, just do the following:

Lab 11: Introduction to D and J-K Flip-Flop - City University of …

This experiment will cover the operation of the two types of edge triggered flip flops: D and JK. Flip flops are different from combinational logic in that their output depends on past and …

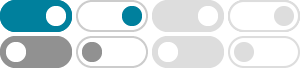

DFFE Primitive - Intel

The DFFE primitive allows you to specify a D-type flipflop with clock enable. Note: When the ENA (clock enable) input is high, the flipflop passes a signal from D to Q . When the ENA input is …