Block Design Objects Block Designs are complex subsystem designs made up of interconnected IP cores, that can either serve as stand-alone designs, or be integrated into other designs. Block Designs, or diagrams, can be created with the IP integrator of the Vivado Design Suite. They can be

The 7 Series FPGAs Integrated Block for PCI Express core is a reliable, high-bandwidth, scalable serial interconnect building block. The core instantiates the 7 Series Integrated Block for PCI Express found in the 7 series FPG As, and supports both Verilog and VHDL. This core simplifies the design process and reduces time to market.

I / O a n d C l o c k P l a n n i n g S t a g e s The Vivado Design Suite facilitates I/O and clock planning at different stages of the design process from initial collaboration between the PCB designer and the FPGA designer to validation

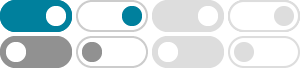

Each block has a background color that indicates the following: Chapter 1: Xilinx Blockset UG958 (v2020.2) November 18, 2020 www.xilinx.com Designing with System Generator 9. Send Fedback e. www.xilinx.com. Organization of Blockset Libraries. Common Options in Block Parameter Dialog Boxes. Block Reference Pages. AXI4 Blocks. Basic Element Blocks

Block Design (BD) Note: In some cases, third-party providers offer IP as synthesized EDIF netlists. You can load these files into a Vivado design using the Add Sources command. The available methods to work with IP in a design are: • Use the Managed IP flow to customize IP and generate output products, including a

S t e p 2 : C r e a t i n g a n I P I n t e g r a t o r D e s i g n. 1. In the Flow Navigator, select Create Block Design. The Create Block Design dialog box opens, as shown in the following figure: Chapter 1: Designing IP Subsystems in IP Integrator UG995 (v2022.1) April 26, 2022 www.xilinx.com Designing IP Subsystems Using IP Integrator 8

P&R Minimal test Exhaustive functional tests Test Bench (System C) Test Bench (System C) RTL (VHDL)C++ code RTL (VHDL) (5k lines)) Test Bench (application) RTL Synth P&R Exhaustive functional tests System-level Debug HLS IPI C Debug Traditional Flow • 240 people*mo o 10 people o 2 years HLS Based Flow • 16 people*mo o 2 people o 8 month HW ...

Distributed Memory Generator - Xilinx

AMD provides a Distributed Memory Generator LogiCORE to help you build on-chip Distributed Memories with SelectRAM quickly and easily.

Block Diagram The ZCU111 board block diagram is shown in Figure1-1. Board Features The ZCU111 evaluation board features are listed here. Detailed information for each feature is provided in Board Component Descriptions in Chapter3. • XCZU28DR-2E, FFVG1517 package • Form factor: rectangular 11.811 in. x 7.874 in. x 0.1 in. • Configuration ...

Slice - Xilinx

The Slice IP core is used to rip bits off a bus net. Often there is a need to rip some bits off a wide bus net. This IP core can be instantiated to accomplish this purpose.